Vacuum heating and heat dissipation measures for antifuse FPGAs

-

摘要: 航天电子元器件工作于真空环境时,必须格外考虑其发热及散热问题。文章对某反熔丝FPGA器件工作于真空环境时温度与功耗的关系及散热措施进行研究。通过热真空试验得到该器件不同散热措施及PCB条件下的发热及散热情况数据,并依据数据分析给出其在真空环境下的散热措施建议。该器件采用了带热沉的陶瓷四侧扁平208引脚封装(CQFP208),在此类较大尺寸封装(瓷体29.2 mm×29.2 mm)中引入大尺寸热沉(23 mm×23 mm)并应用于航天器在国内尚属首次。文章的试验结果及散热措施建议对采用相同或类似封装的电子元器件均有参考作用。Abstract: For aerospace electronic components to be worked in the vacuum environment, the device heating and the related heat dissipation must be specially considered. In this paper, the relationship between the temperature of a certain type of antifuse FPGAs working in the vacuum environment and the power consumption are studied, together with measures of heat dissipation. Through thermal vacuum test, the thermal value and the heat dissipation data of the devices with regard to different heat dissipation measures and various PCB conditions are obtained. Finally, the heat dissipation measures for the devices in vacuum environment are suggested. The device adopts a ceramic four-side flat 208-pin package (CQFP208) with heat sink. It is the first time in China to introduce comparable-sized heat sink (23 mm×23 mm) into such large size package (porcelain 29.2 mm×29.2 mm) and apply it to spacecraft. The test results and the heat dissipation measures proposed in this paper can serve as a reference for the applications of the electronic components with the same or similar kind of package.

-

Keywords:

- electronic components /

- vacuum /

- thermal design /

- thermal conductivity /

- thermal resistance /

- heat dissipation

-

0. 引言

航天器长期工作在复杂恶劣的真空环境中,散热手段有限。其内部温度水平关乎仪器设备和部件功能的发挥、性能指标的实现以及整器的可靠性和寿命等[1-3]。因此,航天器的热控制能力对其在空间应用至关重要。随着航天器功能任务的提高,对热控制系统的控温能力和控温精度要求越来越高[4-9]。然而,系统控温措施往往仅关注整体或者发热量较大的分系统或模块;若要精细到个别局部区域或某个电子元器件时,则需要采取一些有效措施将局部散热与系统散热进行有效连接和组合。

电子设备是航天器内部热量的来源之一。随着电子元器件的性能提升以及集成电路技术的迅速发展,电子元器件的总发热密度大幅增长。若器件的散热能力有限,就会造成自身温度升高,以致性能下降、可靠性变差、寿命缩短等[10-13]。阿伦纽斯模型表明,器件的退化速率随温度呈e指数规律变化,即温度每上升10 ℃,器件寿命缩短一半[14-17]。因此,美国早在20世纪70年代就发布了可靠性热设计手册,要求在整个设计过程中,电子设备设计工程师、热设计工程师和可靠性工程师密切合作,将热管理贯穿于电子系统和设备设计生产的全过程[18]。我国国家国防科技工业委员会也在1992年7月颁布了GJB/Z 27—1992《电子设备可靠性热设计手册》[19],为军用电子设备热设计提供了基本理论和方法;1993年9月颁布了GJB/Z 35—1993《元器件降额准则》[20],规定了各种元器件在不同应用情况下应降额的参数和量值。合理的热设计可以减少元器件,尤其是真空环境中的电子元器件的失效,因此有必要对真空环境下的器件发热及散热特性进行分析,以便为后端热设计提供参考。

反熔丝FPGA因其较高的可靠性和反熔丝本身对辐照免疫而被广泛应用于各种航天器[21-23]。早期国内外航天器所需的FPGA产品均来自美国的Actel公司,而当前为应对西方对我国的技术封锁和核心元器件禁运,亟需实现反熔丝FPGA产品的国产化。国产10万门反熔丝FPGA内部时序逻辑(R单元)采用了三模冗余,质量等级对标Actel公司宇航最高等级(V级)产品,采用了带热沉的陶瓷四侧扁平208引脚封装(CQFP208)。在此类较大尺寸封装(瓷体29.2 mm×29.2 mm)中引入大尺寸热沉(23 mm×23 mm)并应用于航天器在国内尚属首次,且对于带热沉封装的反熔丝FPGA的装配和散热方式无任何资料可借鉴。由于该器件自带热沉,最好的散热措施应为直接将热沉焊接到印制电路板(PCB)上,然而这种方法只适用于代码和技术状态均已固化的成熟产品;另外,在实际使用中,某些应用场合该器件的功耗并不大,无须散热处理。因此,为了合理使用该器件,应当首先确定其必须进行散热处理的临界功耗,再找到不对热沉进行焊接的其他散热措施。本文通过热真空试验对反熔丝FPGA器件的真空发热特性进行研究,以确定合理、有效的散热措施。

1. 试验对象和方法

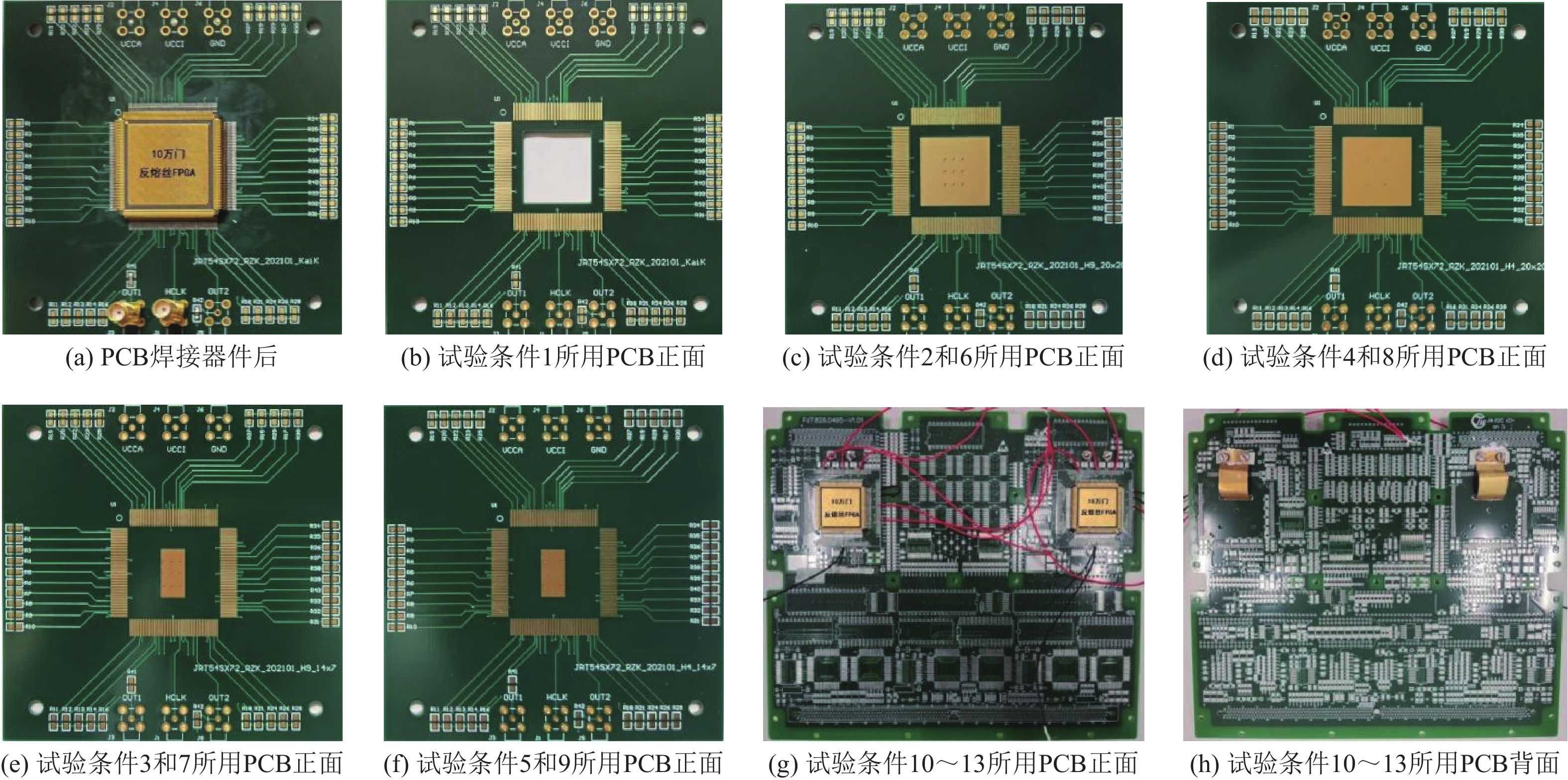

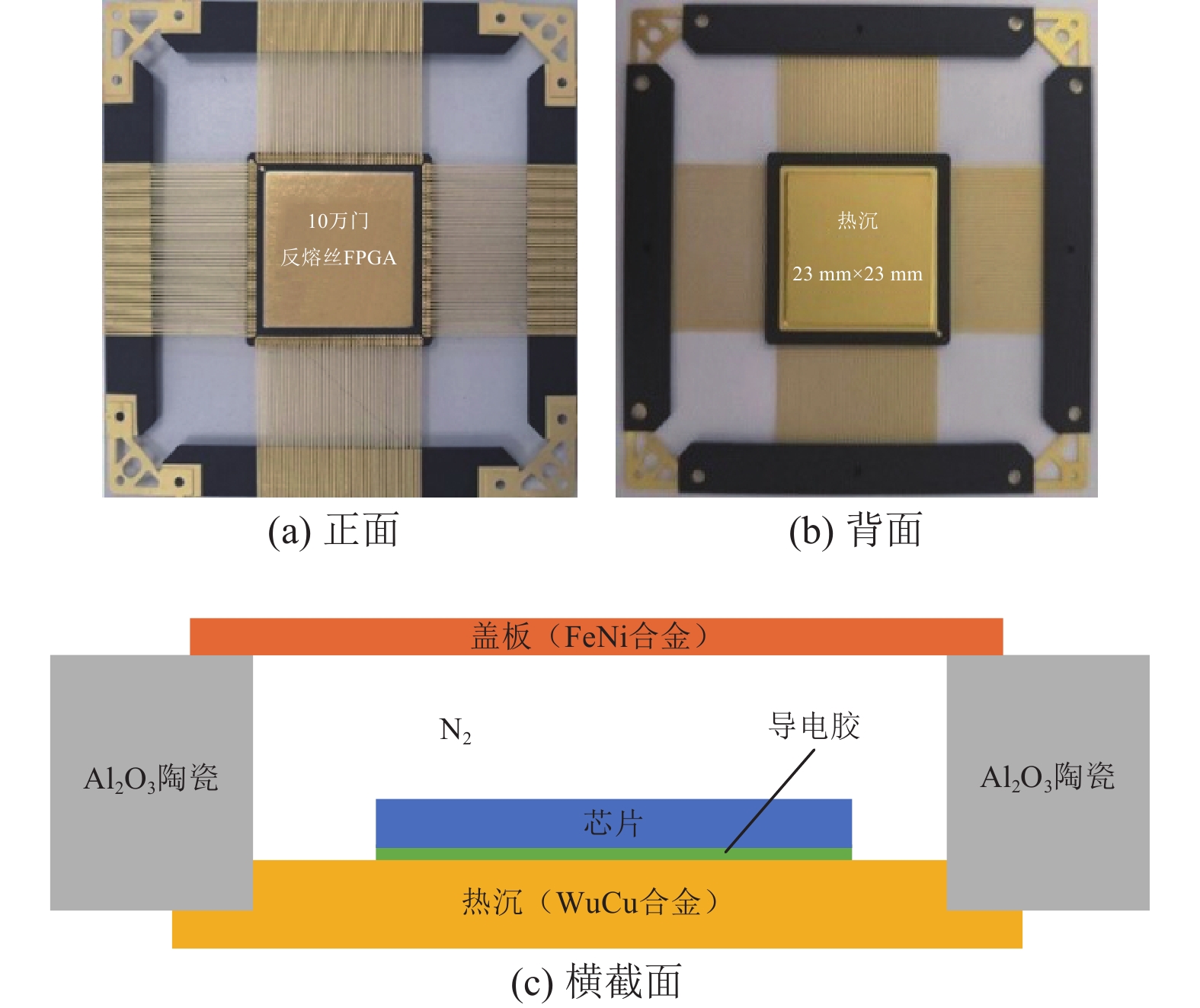

试验器件选用某国产10万门反熔丝FPGA,其正、背面照片如图1(a)、(b)所示,图1(c)为其横截面示意。芯片与热沉通过导电胶黏结,热沉为WuCu合金,是导热系数为191 W/(m∙K)的高导热材料,厚度为1 mm,面积为23 mm×23 mm。

试验过程中,将器件置于真空度优于1.3×10-3 Pa的真空罐中,用加热丝模拟热辐射源,通过测控设备稳定试验条件。为使试验样品产生递增功耗,采用外部信号源提供频率递增的工作时钟。通过热电偶温度传感器测试样品电路顶部盖板中央或底部热沉中央的温度代表器件温度。热电偶端头为直径8 mm的圆形平面,通过导热胶GD480与被测点紧密黏结。试验时器件处于工作状态,端口电压VCCI和内核电压VCCA分别设置为5.5 V和2.75 V(为了产生较大功耗,均较典型工作电压超出10%)。器件编程后的资源利用率为93.49%。

试验条件及样品分配情况如表1所示。其中在焊盘上打通孔是为了将热量从焊盘传导到2 mm厚的PCB的地平面并散发出去。试验过程中,每次增大功耗后须等待器件温度上升且稳定后记录盖板和热沉温度数值(试验条件2~13中由于空间关系无法测量热沉温度,仅测量盖板温度),再进行下一次增大器件功耗的操作。

试验用PCB如图2所示。

表 1 试验条件及样品分配情况Table 1. Test conditions and sample allocations试验

条件PCB面积/

cm热沉下方PCB上焊盘 热沉处理方式 所用PCB

照片面积/mm 通孔数量 1 9.25×9.0 无焊盘

(PCB开窗)裸露 图2(b) 2 9.25×9.0 20×20 9 焊接到PCB 图2(c) 3 9.25×9.0 14×7 9 焊接到PCB 图2(e) 4 9.25×9.0 20×20 4 焊接到PCB 图2(d) 5 9.25×9.0 14×7 4 焊接到PCB 图2(f) 6 9.25×9.0 20×20 9 与PCB之间加导热绝缘垫 图2(c) 7 9.25×9.0 14×7 9 与PCB之间加导热绝缘垫 图2(e) 8 9.25×9.0 20×20 4 与PCB之间加导热绝缘垫 图2(d) 9 9.25×9.0 14×7 4 与PCB之间加导热绝缘垫 图2(f) 10 30×25 无焊盘 通过0.2 mm厚铜带连接到PCB 图2(g)(h) 11 30×25 无焊盘 通过0.1 mm厚铜带连接到PCB 图2(g)(h) 12 30×25 无焊盘 0.2 mm厚铜带断开与PCB的连接(该端悬空),另一端仍保持与热沉的焊接状态 图2(g)(h) 13 30×25 无焊盘 0.1 mm厚铜带断开与PCB的连接(该端悬空),另一端仍保持与热沉的焊接状态 图2(g)(h) 2. 试验结果与分析

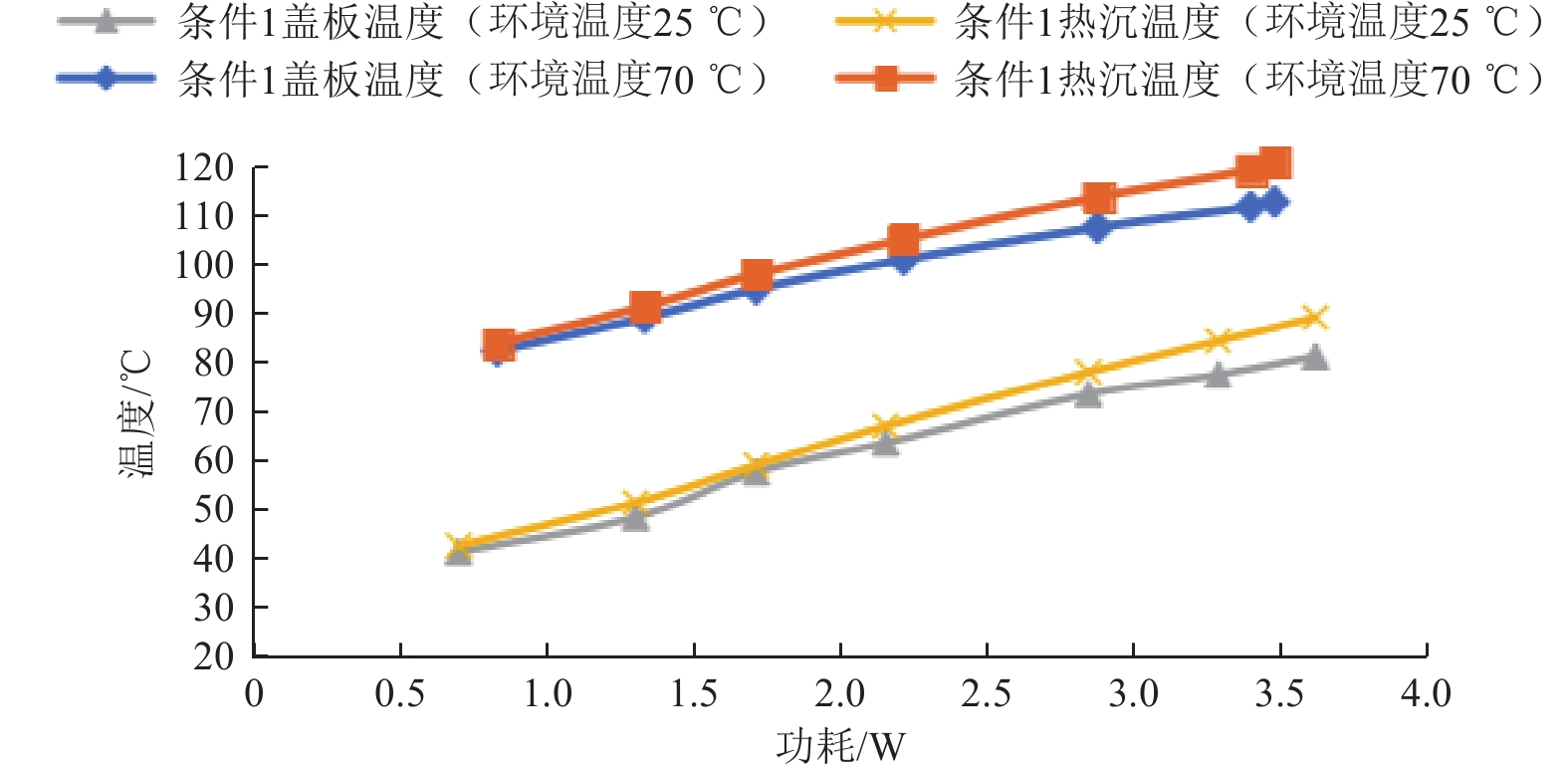

在试验条件1下,器件散热只有2种途径:其一为器件自身热辐射;其二为热量通过208个引脚传到PCB,再从PCB经过热辐射散发出去,散热效果与PCB面积直接相关。试验过程中通过热电偶对每次增大功耗后的器件盖板和热沉温度进行测量,结果如图3所示,其中每次温度重新达到平衡的时间不超过11 min。

在航天工程应用中,应按照GJB/Z 35—1993《元器件降额准则》的要求对元器件降额使用,其中要求航天器与战略火箭降额等级至少为Ⅰ级,在此要求下MOS集成电路结温最高不能超过85 ℃。根据图3,器件功耗为0.97 W时其热沉温度达到85 ℃;而结–热沉间的热阻仅为0.56 ℃/W,因此芯片结温约等于热沉温度,即可以认为在该试验条件下,若要满足Ⅰ级降额要求,则器件功耗不能超过0.97 W;若想提升功耗,则必须要有更好的散热措施。从图3中也可以看出,随着功耗升高,热沉与盖板之间的温差越来越大,这是由于结–盖板间的热阻(5.41 ℃/W)远大于结‒热沉间的热阻,随着功耗的增加,散热热流越来越大所致。

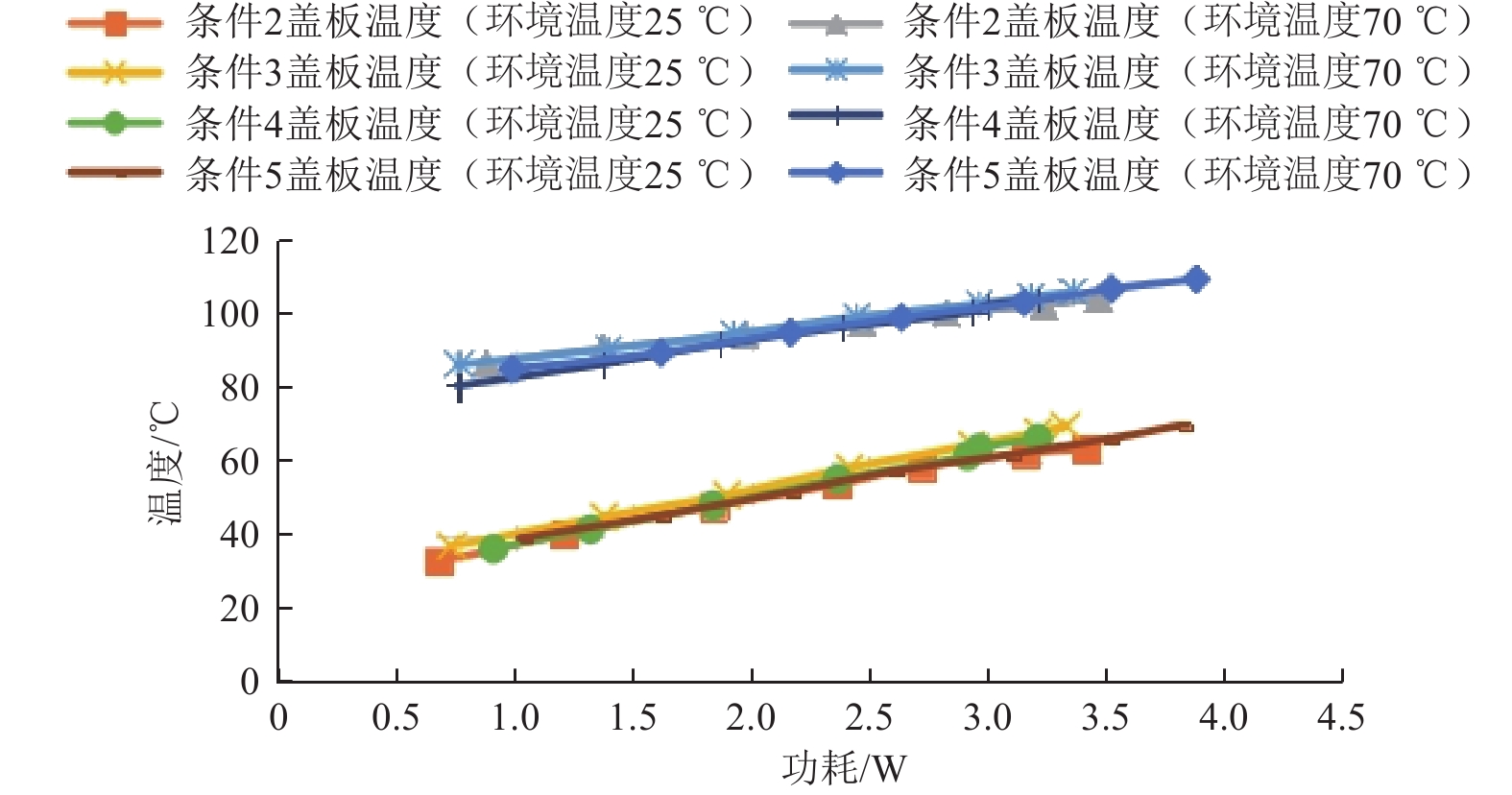

试验条件2~5下,器件盖板温度随功耗的变化如图4所示。这4种条件均为热沉直接焊接到PCB上,但热沉下方的焊盘面积和通孔数量不同。从图4可以看出,4种条件下盖板温度在统计学意义上相差不大,表明盖板温度与焊盘面积、通孔数量关系不大。这并不符合最初的预期,因为理论上焊盘越大、通孔数量越多,越有利于器件将热量传导到PCB进行散热。分析其原因认为,在真空模拟环境中,热量传递按照“芯片→热沉→焊盘→PCB→真空腔体模拟环境”和“芯片→管壳和盖板→真空腔体模拟环境”链条进行,其中“芯片→热沉→焊盘→PCB”和“芯片→管壳和盖板”均主要靠热传导进行热量传递,传递效率高;而最后一环“PCB→真空腔体模拟环境”和“管壳和盖板→真空腔体模拟环境”靠热辐射进行散热,散热效率低,成为散热的“瓶颈”。而在实际的航天器热设计中,PCB连接金属机壳(器件也可以通过在盖板上安装散热片、导热锁等连接机壳),机壳的热量通过系统散热措施直接散到航天器外部真空黑冷环境中,其散热效率比本试验中的最后散热环节(热辐射)效率高得多。本试验受条件所限,无法模拟航天器的系统散热,但可证明热沉下方焊盘面积、通孔数量均不是器件散热过程中的“瓶颈”。比较试验条件6~9下器件盖板温度随功耗的变化(图5),可以得出相同的结论。

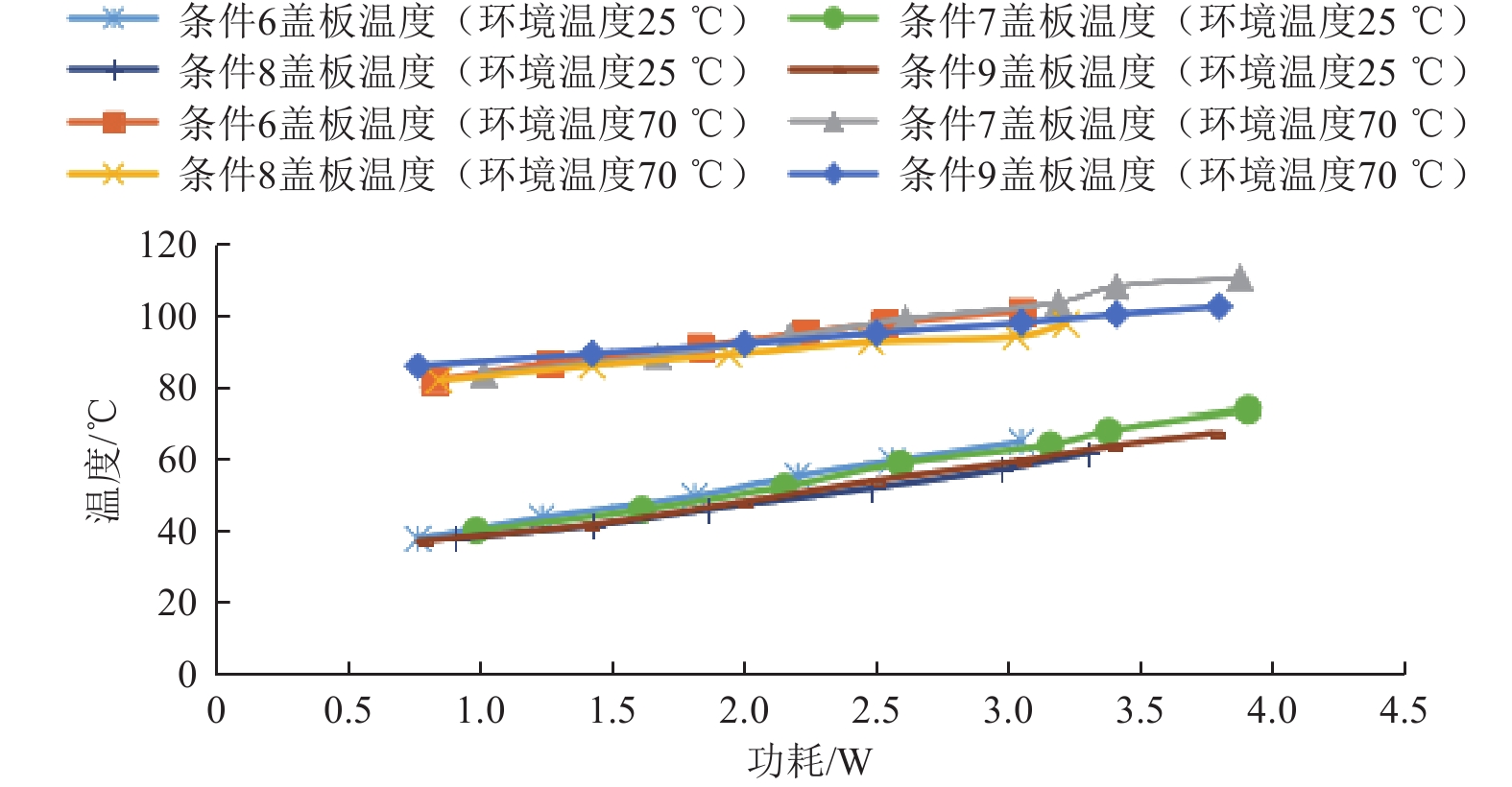

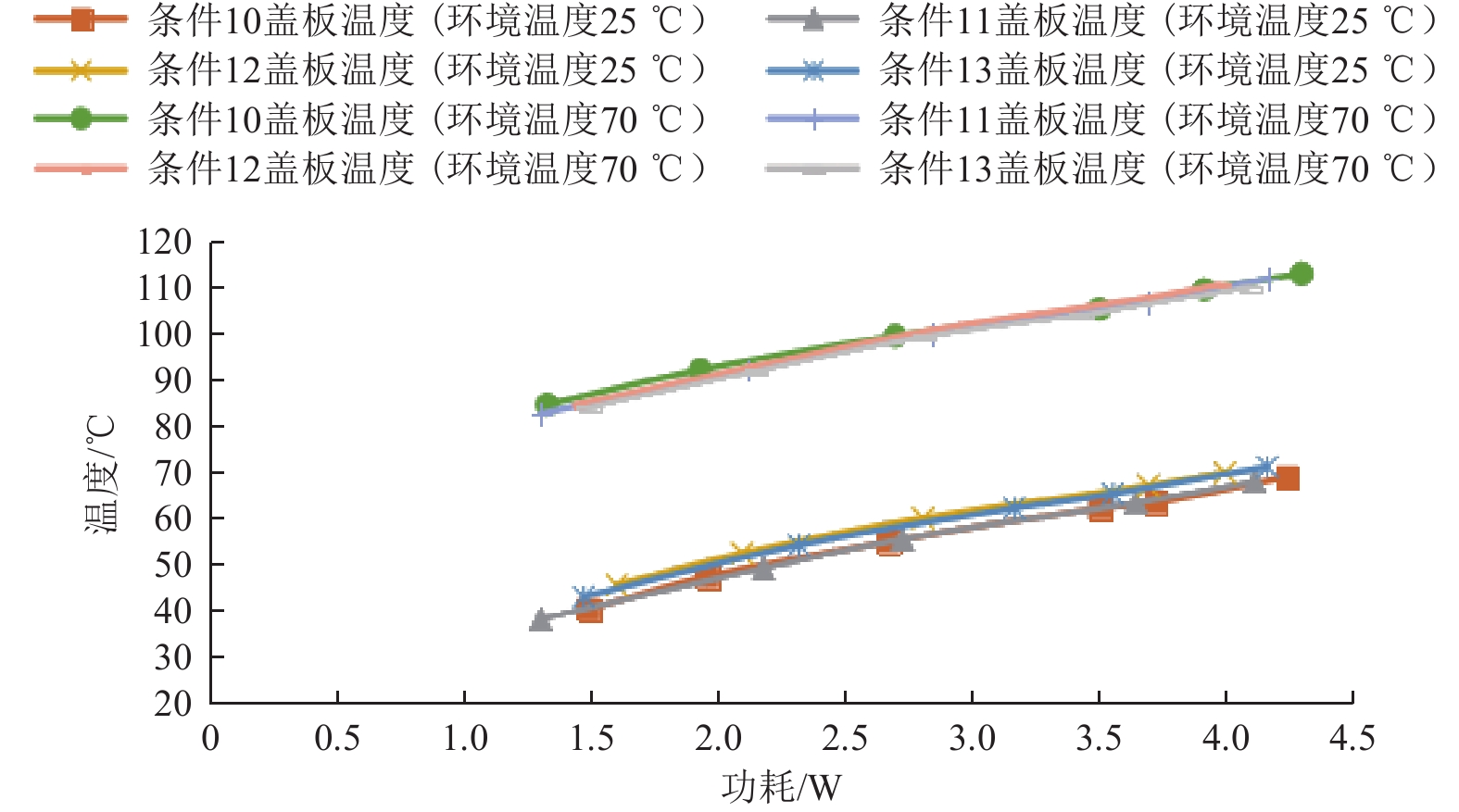

比较试验条件10~13下器件盖板温度随功耗的变化,如图6所示。其中,条件10和11为热沉通过铜带(厚度分别为0.2 mm和0.1 mm)与PCB连接散热,条件12和13为铜带保持与热沉的连接但与PCB断开接触的情况。

由图6可以看出:

1)采用0.2 mm或0.1 mm厚铜带在器件散热效果方面无明显区别;

2)铜带是否断开与PCB的接触对器件散热效果影响不明显,环境温度为25 ℃时两者间大约有3 ℃差异,而环境温度为70 ℃时已无明显差异,其主要原因为热辐射强度与温度的4次方成正比[24],随着温度升高,铜带本身的热辐射显著增强。

另外,与条件2~9相比,条件10~13下的PCB面积大大增加但并未显著加快散热速度,因为PCB地平面中距铜带接触点越远的地方温度越低,且温度从地平面传导到PCB表面再进行热辐射这一环节中的热传递效率较低(PCB板材质为FR-4,导热系数较小,为0.2 W/(m∙K)),所以PCB上距接触点较远处的散热可忽略不计。

3. 结论与建议

本文通过热真空试验,探索了采用带热沉封装的反熔丝FPGA器件在真空环境下功耗与器件温度之间的关系,以及器件温度与PCB面积、热沉散热方式、PCB上热沉焊盘面积、焊盘与地平面之间通孔数量的关系,得到如下结论与建议:

1)在PCB面积为9.25 cm×9.0 cm、无散热措施、器件结温达到85 ℃时,功耗约为1 W。此数据可作为在实际应用时是否须对器件作散热处理的参考临界值。

2)在该试验中热沉与PCB之间采用焊接或导热绝缘垫对散热效果影响不大,热沉焊盘面积及焊盘与地平面之间通孔数量对散热效果也影响不大,但为了达到更快的散热速度,仍建议在航天装联工艺规则范围内尽量扩大热沉下方焊盘的面积并适当增加焊盘到地平面的通孔数量,且通孔应尽量分布在焊盘边缘。另外,建议选用高导热率的PCB,并将PCB连接到结构件以对接系统散热连接。

3)实际航天器系统控温措施可靠性较高,其内部电子元器件工作环境温度可控制在0~25 ℃范围。因此可考虑将与器件热沉连接的铜带另一端直接通过导热绝缘垫连接到机壳进行散热。

4)若FPGA底部PCB无走线或背部无其他元器件,热沉通过PCB开窗及导热绝缘垫直接连接到金属机壳的方案也是非常有效的散热方式。

5)在实际使用过程中也可考虑其他散热措施,例如通过盖板散热,可在盖板上安装通过绝缘措施连接到结构件的散热片或导热锁等。

6)发射率是辐射换热的重要参数,为增加结构面到真空腔体的辐射换热,可考虑采用涂黑等方式。

本次实验由于条件所限未采用系统散热措施,对元器件和PCB的散热造成了一定的限制,后续将配合热传导和辐射仿真软件进行先期分析,进一步完善该实验。

-

表 1 试验条件及样品分配情况

Table 1 Test conditions and sample allocations

试验

条件PCB面积/

cm热沉下方PCB上焊盘 热沉处理方式 所用PCB

照片面积/mm 通孔数量 1 9.25×9.0 无焊盘

(PCB开窗)裸露 图2(b) 2 9.25×9.0 20×20 9 焊接到PCB 图2(c) 3 9.25×9.0 14×7 9 焊接到PCB 图2(e) 4 9.25×9.0 20×20 4 焊接到PCB 图2(d) 5 9.25×9.0 14×7 4 焊接到PCB 图2(f) 6 9.25×9.0 20×20 9 与PCB之间加导热绝缘垫 图2(c) 7 9.25×9.0 14×7 9 与PCB之间加导热绝缘垫 图2(e) 8 9.25×9.0 20×20 4 与PCB之间加导热绝缘垫 图2(d) 9 9.25×9.0 14×7 4 与PCB之间加导热绝缘垫 图2(f) 10 30×25 无焊盘 通过0.2 mm厚铜带连接到PCB 图2(g)(h) 11 30×25 无焊盘 通过0.1 mm厚铜带连接到PCB 图2(g)(h) 12 30×25 无焊盘 0.2 mm厚铜带断开与PCB的连接(该端悬空),另一端仍保持与热沉的焊接状态 图2(g)(h) 13 30×25 无焊盘 0.1 mm厚铜带断开与PCB的连接(该端悬空),另一端仍保持与热沉的焊接状态 图2(g)(h) -

[1] 苗建印, 钟奇, 赵啟伟, 等. 航天器热控制技术[M]. 北京: 北京理工大学出版社, 2018: 3 [2] CHOI M K. Using paraffin PCM for thermal management of BOLAS planetary CubeSats with ion thrusters[C]//AIAA Propulsion and Energy 2019 Forum. Indianapolis, IN, USA, 2019

[3] IWATA N, USUI T, IKEDA M, et al. Evaluation of in-orbit thermal performance of X-ray astronomy satellite “Hitomi”[J]. Journal of Spacecraft & Rockets, 2017, 55(1): 77-84

[4] GILMORE D G. Spacecraft thermal control handbook: Volume I: fundamental technologies[G], 2002: 21-94

[5] MURTHY H S V, SHARMA A K, BADARINARAYANA K, et al. Thermal management of GEO satellite communication payload[C]//2011 IEEE International Vacuum Electronics Conference (IVEC). Bangalore, India, 2011: 469-470

[6] 刘欣, 梁新刚. 多辐射器航天器热控流体回路布局的(火积)耗散分析[J]. 宇航学报, 2019, 40(2): 231-238 LIU X, LIANG X G. Entranspy dissipation analysis of spacecraft thermal control fluid loop layout with multiple radiators[J]. Journal of Astronautics, 2019, 40(2): 231-238

[7] 刘欣, 梁新刚. 可展开式辐射器热控对航天器轨道调整的适应性分析[J]. 宇航学报, 2021, 42(3): 390-396 LIU X, LIANG X G. Adaptability analysis of deployable radiator thermal control system to spacecraft orbit adjustment[J]. Journal of Astronautics, 2021, 42(3): 390-396

[8] 张秀, 张昊春, 刘秀婷, 等. 空间核电源热管式辐射散热器热分析与参数优化[J]. 宇航学报, 2019, 40(4): 452-458 ZHANG X, ZHANG H C, LIU X T, et al. Thermal analysis and parameter optimization of a heat-pipe radiator for space nuclear power[J]. Journal of Astronautics, 2019, 40(4): 452-458

[9] 杜卓林, 江海, 陈少华, 等. 上面级发射中高轨道卫星外热流分析[J]. 宇航学报, 2018, 39(10): 1107-1115 DU Z L, JIANG H, CHEN S H, et al. Analysis of external heat flux for MEO and GEO satellite on upper stage launch orbit[J]. Journal of Astronautics, 2018, 39(10): 1107-1115

[10] MAHALINGAM M. Thermal management in semiconductor device packaging[J]. Proceedings of the IEEE, 1985, 73(9): 1396-1404 DOI: 10.1109/PROC.1985.13300

[11] 邢旭东, 陈怀超. 功率器件在真空环境中的热分析及研究[C]//2007年机械电子学学术会议. 昆明, 2007: 323-328 [12] TAUB H, SCHILLING D. Digital integrated electronics[M]. NewYork: McCraw-Hill, 1977: ch. 1: 5-6

[13] CARR W N, MIZE J. MOS/LSl design and application [M]. New York: McCraw-Hill, 1972: ch. 3: 85-89

[14] Failure mechanisms and models for semiconductor devices: JEDEC JEP122H-2016[S], 2016: 2

[15] OZMAT B. Interconnect technologies and the thermal performance of MCM[J]. IEEE Transactions on Components, Hybrids, and Manufacturing Technology, 1992, 15(5): 860-869 DOI: 10.1109/33.180052

[16] PECK D S. The analysis of data from accelerated stress tests[C]//9th Reliability Physics Symposium. Las Vegas, NV, USA, 1971: 69-78

[17] COOPER M S. Investigation of Arrhenius acceleration factor for integrated circuit early life failure region with several failure mechanisms[J]. IEEE Transactions on Components and Packaging Technologies, 2005, 28(3): 561-563 DOI: 10.1109/TCAPT.2005.848581

[18] WALLACE W Jr, HAUMESSER R. Reliability/design thermal applications: MIL-HDBK-251[S], 1973: 10

[19] 电子设备可靠性热设计手册: GJB/Z 27—1992[S], 1992 [20] 元器件降额准则: GJB/Z 35—1993[S], 1993 [21] ZHANG G, HU C, YU P, et al. Characteristic voltage of programmed metal-to-metal antifuses[J]. IEEE Electron Device Letters, 1994, 15(5): 166-168 DOI: 10.1109/55.291598

[22] ZHANG G, KING Y, ELFOUKHY S, et al. On-state reliability of amorphous silicon antifuses[C]//Proceedings of International Electron Devices Meeting. Washington DC, USA, 1995

[23] REZGUI S, WANG J J, SUN Y M, et al. SET characterization and mitigation in RTAX-S antifuse FPGAs[C]// 2009 IEEE Aerospace Conference. Big Sky, MT, USA , 2009

[24] 郭文强. 航天器电子元器件胶粘散热设计研究[D]. 西安: 西安电子科技大学, 2020: 9-10 -

期刊类型引用(1)

1. 王相昂,马诗洋,刘悦,李永佳. 基于MLVDS接口电路在波控系统中的应用. 电子设计工程. 2023(17): 90-94 .  百度学术

百度学术

其他类型引用(0)

下载:

下载: